# Direct Digital Synthesizer VFO By C. V. Niras/VU3CNS

cvniras@hamradio.in

**T**his is a continuation of my previous DDS projects. This project uses PIC16F628A and AD9850 or AD9851. PIC16F628A is an 18-Pin microcontroller with 2K byte program memory, it is a FLASH-based and a member of the versatile PIC16F62XA family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers. PIC16F62XA devices have special features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption.

# Features

- 1. Range 0 to 70 MHz by 1 Hz step.

- 2. Freq setting in 1, 10, 100Hz, 1, 10, 100KHz, 1, 10 MHz by using a low cost mechanical encoder with a variable tuning rate.

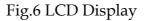

- 3. 2 rows X 16 character LCD display.

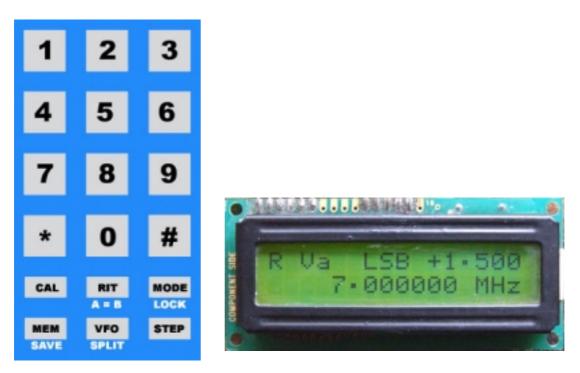

- 4. A 4 x 3 Keypad used for easy freq entry.

- 5. IF, CW, SSB offsets settings when used with Transceiver/ Receiver.

- 6. Software calibration to WWV or equivalent.

- 7. Two VFOs and split freq operation.

- 8. 19 user memories, memories freq + mode (i.e. LSB/USB etc.)

- 9. All settings are held in EEPROM and are permanent (but user can change it any time).

- 10. 4 Band selection and 4 Mode selection outputs.

- 11. When operating below IF frequency, clockwise rotation of rotary encoder decreases DDS out put frequency but increases the display frequency.

- 12. RIT operation.

# DDS

The AD9851 is a highly integrated device that uses advanced DDS technology to form a digitally programmable frequency synthesizer. AD9851 generates a stable frequency and phase-programmable digitized analogue output sine wave. This sine wave can be used directly as frequency source with an output tuning resolution of approximately 0.04 Hz with a 180 MHz system clock. The AD9851 contains 6 X REFCLK Multiplier circuits that eliminate the need for a high speed reference oscillator.

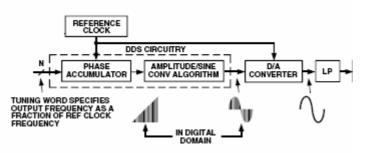

Fig. 1 Basic DDS Block Diagram

The basic block diagram is shown in Figure 1. The frequency out put can be calculated using the following formulae

Fout = ( $\Delta$  Phase X System Clock)/ 2 ^ 32

Where:

$\triangle$  Phase = decimal value of 32 bit tuning word System Clock = REFCLK frequency in MHz or 6 X REFCLK frequency (in MHz) if the 6 X REFCLK Multiplier is enabled Fout = Output frequency of DDS in MHz

The DDS circuitry is basically a digital frequency divider function whose incremental resolution is determined by the frequency of the system clock, and N (number of bits in the tuning word). The phase accumulator is a variable-modulus counter that increments the number stored in it each time it receives a clock pulse. When the counter reaches full-scale it wraps around, making the phase accumulator's output phase-continuous. The frequency tuning word sets the modulus of the counter, which effectively determines the size of the increment ( $\Delta$ Phase) that will be added to the value in the phase accumulator on the next clock pulse. The larger the added increment, the faster the accumulator wraps around, which results in a higher output frequency.

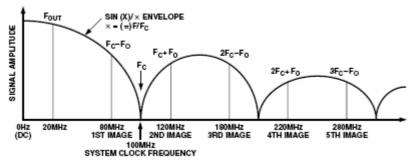

Fig. 2 Output Spectrum of DDS

In the example shown in Figure 2, the system clock is 100 MHz and the output frequency set to 20 MHz. A low pass filter is essential to remove unwanted images. A good rule-of-thumb is limiting the output frequency to

2

1/3<sup>rd</sup> of System Clock frequency. One can use the other images also with help of a good band pass filter. Note that these images are not harmonics and it keeps a 1:1 relation with the fundamental frequency, i.e. if fundamental frequency increased 1 Hz then the image frequency also shifted 1 Hz.

# Construction notes.

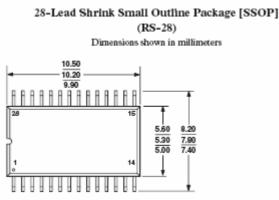

The most difficult task is soldering AD9851 in the PCB. AD9850 or AD9851 is in SSOP package with 28 pins as shown in Fig3. Use a magnifying glass and a point soldering iron to the job neatly.

Fig. 3 Dimensions of AD9851BRS

A Commonly available 2 line x 16 character LCD (using Hitachi HD44780 controller) with or without R/W pin (software uses delays rather than busy checks) is used to display frequency and messages. LCD contrast can be adjusted using 10K pot, turn towards ground to increase contrast.

After assembling recheck all wiring for dry solders, loose connections etc. PCB may be cleaned with isopropyl. Use good IC base for the microcontroller.

Hex file for programming PIC16F628A is available on website <u>www.hamradioindia.org</u>, a simple Multi PIC programmer circuit and software for programming PIC can also download from the site. If required the author can supply programmed PIC at a nominal rate.

# Calibration and setup screens

This is provided to change VFO configurations according to the needs of end user. Press down the calibration button on start-up to enter this screen. The followings can be set one by one; a brief press of calibration button will change to the next, and finally saves all changes or settings.

# 1. Enable or disable internal multiplier

This is only for AD9851, because AD9850 hasn't any internal multiplier, for AD9850 always disable the internal multiplier. The internal multiplier multiplies the DDS crystal frequency by 6. Use rotary encoder for selection.

# 2. DDS system clock

It sets the DDS VFO to produce 10MHz and displays the DDS system clock. The DDS system clock should be set to the DDS crystal frequency, for

the AD9850 or AD9851 with internal multiplier disabled, and 6 times of DDS crystal frequency for AD9851 with the internal multiplier enabled. Use keypad or rotary encoder to make changes until the VFO output is exactly 10MHz. This is required because in most cases the DDS crystal oscillates at a frequency slightly differed from its printed value.

### **3. Max DDS frequency**

It is the high limit of the DDS output frequency; maximum limit is  $1/3^{rd}$  of DDS system clock or cut of frequency of the band pass filter. The software doesn't allow going beyond this limit, but keeps in mind that SSB or CW offset will be added after checking this limit.

#### 4. Minimum DDS frequency

As the maximum limit, this is the minimum limit of DDS frequency. Here negative values can be set, only recommended for when it is necessary to get a frequency less than display offset frequency (see functional description for more details).

#### 5. SSB offset

It is the sideband shift, usually set to a half of the SSB crystal filter. Negative values are also valid; a negative offset simply changes the meaning of LSB and USB.

#### 6. CW offset

It is the side tone frequency for CW; default is 800Hz because most peoples preferred this frequency. The CW offset will not add on transmitting, and in receiving the VFO frequency will be shifted by this value.

All done, just press calibration to save all the changes. The message "SAVING" will be displayed at the end if anything changed. A time out of 10 seconds has been provide except in setting of DDS system clock, in timeout all changes are discarded and return to VFO screen.

# **Functional Description**

The DDS chip contains 40 bit register that stores 32 bit frequency control word and 5 bit phase modulation word and 6 x reference clock multiplier enable (not implemented on AD9850), and the power down function. This register can be loaded in parallel or serial mode, and serial mode is selected, hence only three pins are required. The frequency control word is calculated by multiplying required frequency with the DDS calibration constant stored in EEPROM. 3 bytes are used to represent decimal values of DDS calibration constant for greater accuracy.

The LCD is wired in 4 bit mode, so that other pins of LCD's are left unused. Software uses delays rather than busy checks, so LCD with or without R/W pin can be used.

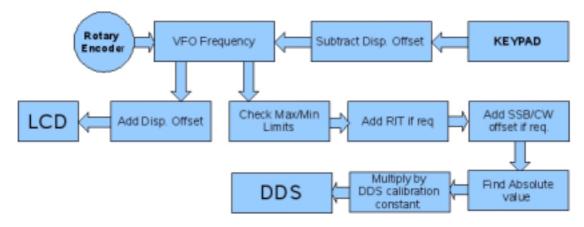

The working of software is illustrated in the Fig given below.

#### Fig. 4 functions of the software

VFO frequency is incremented on turning rotary encoder turning clockwise. Display offset is added to this frequency and displayed. Display offset is removed from the value entered through the keypad.

The software allows negative values in RX minimum frequency; this required only when it is needed to operate VFO below the "display offset" frequency. At this time, the clockwise rotation of rotary encoder decrements DDS output frequency while incrementing displayed frequency. For example, let the IF frequency be 9 MHz and need to operate on 40M band as lower side injection. So the VFO frequency should be 1.9 to 2.0 MHz. Set the display offset as 9MHz in the calibration screen. While entering 7MHz through keypad, it removes display offset, and the result, i.e. VFO frequency is - 2MHz. Before sending to LCD, the display offset, i.e. 9MHz is added so -2 + 9.0 = 7.0 is displayed. While turning rotary encoder clock wise, it incremented towards -1.9, so the display frequency is incremented from 7 to 7.1 (-1.9 + 9 = 7.1), but before sending to DDS, it finds absolute value of VFO frequency so that the DDS out put frequency is decreased from 2.0 to 1.9 MHz. The maximum and minimum checking are always done on VFO frequency, so it is necessary to set the RX minimum frequency at the most possible minimum frequency (-2.0 in this example). If this is operated on 20M band, then the VFO frequency should be 5 to 5.450 MHz, so displayed frequency is increases from 14.0 to 14.450MHz, also DDS frequency is increases from 5.0 to 5.450MHz, i.e. both are increasing. To operate as higher side injection; set display offset as -9.0MHz, now DDS frequency varies from 16.0 to 16.1 for 40M, and from 23.0 to 23.450MHz for 20M.

RIT and CW/SSB offsets are added if the corresponding modes are active. RIT displays separately with sign, it will not be discarded until power off. The microcontroller memorises modes, frequency etc, and started in the previous state on power up.

# **Operational use**

On power up the software version number is displayed for a short time. The second digit after decimal point will be 6 if the internal multiplier of AD9851 enabled else it will be 1.

For ease of operation Keypad, rotary encoder and other six buttons are provided. The "\* "key represent the decimal point and "# "used to "enter" the value. For an example; to enter 7.5 MHz, first press 7, the "\* "key then 5 followed by "#" – the "Enter key ". The frequency will be displayed as "7.500000 MHz". When pressing any key in the keypad the same will be displayed in the LCD and the "MHz" text in the LCD has been change to "#" as a reminder to "#" key must be used after the frequency typed in. Press "#" key first to enter a negative value, only allowed in some setup/calibration screens.

Fig. 5 Keypad

Some push buttons have two functions, indicated below on each buttons. To access these function press down the key for 1 second.

Turn the rotary encoder clockwise increases the frequency and anticlockwise decreases it. While pressing down the STEP button a cursor is displayed under one digit. This indicates the selected step size, and to change, turns the rotary encoder while pressing down the STEP button. The software also monitor how fast you turn the knob, if you turn fast the frequency will be increasing a value higher than 1 and up to 30. Due to the software takes 4mS to de-bounce the encode position; if turn so fast then no change will occur. Any changes in the frequency will write into the EEPROM two seconds after stopping the rotary encoder or entering frequency by Keypad. On power up last the frequency stored in the EEPROM will be displayed.

### Managing two VFOs

A VFO button is used to swaps over two VFOs, i.e. VFO A and VFO B. Both frequency and modes (i.e. AM/CW/LSB/USB) associated with the VFO are swapped over with a brief press of VFO button. "VFOA" or "VFOB" is displayed in the LCD.

A = B function will copy the current VFO frequency to the other. A lock has been provided in the software for both keypad and rotary encoder. **Split**

Press down VFO button for 1 second will activate SPLIT mode. In this mode VFO will change from one to another on pressing the PTT and backs when releasing it. A "=>" will be displayed on LCD to indicate SPLIT mode. **RIT**

If the RIT button is pressed briefly, RIT frequency is displayed on the LCD and activate RIT mode. RIT frequency can be changed as long as it does not cross the limits i.e. +/- 3KHz. Pressing the RIT button again, removes the RIT frequency display and the deactivates RIT.

# AM/CW/LSB/USB

Pressing SSB button briefly change the mode one by one. AM, CW, LSB, USB can be selecting by using this. In CW mode CW offset will be added if the VFO in the RX mode and no offset will be add if the VFO in TX mode. In LSB mode SSB offset subtract from the output frequency and add in USB mode. The negative offset just changes the meaning of LSB and USB (see calibration and setup screens for more details). The CW, LSB, or USB displayed on LCD if anyone of these modes is selected.

# Memory mode

Memory function has been used to save and recall RX frequencies to EEPROM. Maximum 19 numbers of frequencies can be saved along with the mode. A brief press of memory button will change from VFO mode to Memory mode and backs. On pressing memory button last operated memory channel will be displayed, and can select the desired memory with the rotary encoder. If the memory frequency is invalid a "---" will be displayed instead of MEM in the LCD. This happens when change something in setup screens and try to recall old memory locations. For example if set maximum RX frequency to 30MHz and select a memory locations stored 40MHz.

To save a VFO frequency in to memory, press MEM buttons for 1 sec, then select memory location using rotary encoder. To avoid erasing any useful frequency the frequency in that location will be displayed on the second line of LCD. Press MEM button after selecting the desired location for 1 sec. A message "SAVE" will be displayed on LCD. If didn't like to overwrite the previous memory Frequencies then a brief press of MEM button helps to back to VFO mode.

There are two methods to go back VFO mode from memory mode. A brief press change to VFO mode and recall the previous VFO frequency. If MEM button is pressed for 1 second then the memory frequency will be copied to VFO and change to VFO mode.

### <u>Acknowledgements</u>

I was able to finish the project help and encouragements given to me by VU2ITI / Prof. T.K. Mani, VU3WIJ / Shaji.P.B, and my colleague A.P. Manoj.

C.V.Niras