## **Hybrid Charge Sensitive Preamplifier**

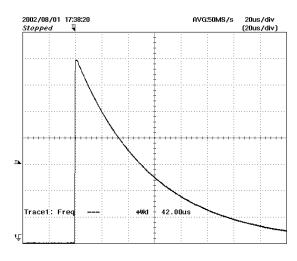

Output using photodiode pulser, 100mV/div, 20usec/div. Time constant (1/e time) ~58 usec

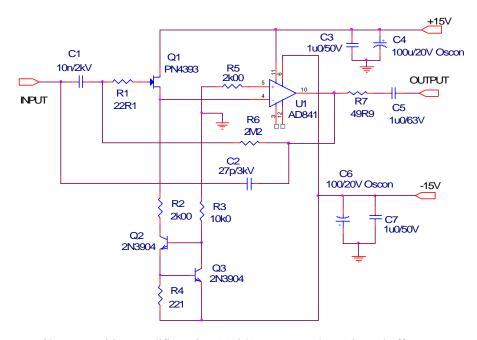

Charge sensitive amplifier using AD841 op amp and FET input buffer

The schematic above shows a hybrid charge sensitive amplifier constructed with a fast bipolar operational amplifier (AD841JN) and a JFET source follower. The opamp provides high loop gain and wide bandwidth, but the inputs are relatively low impedance and require a high bias current The addition of the source follower to the front end results in high input impedance. The source follower JFET, (Q1) is biased at 3ma by an NPN current source (Q2,3). R6 provides global DC feedback and resets charge storage capacitor C2. C1 provides DC isolation for the Q1 gate. It is located inside the AC feedback loop to counteract the effects of the Q1 input and stray capacitance. R7 isolates the amplifier output from capacitive loading (such as a few feet of coaxial cable) that could otherwise cause instability. The output response of the amplifier is shown above. The input was driven with a photodiode pulser to simulate input from a current mode sensor such as a photomultiplier tube or semiconductor detector. The theoretical time constant of the output decay is 59 microseconds, the product of C2 and R6. The actual fall time of the waveform above is measured as the time it takes the voltage to decay from its peak value (700mV) to 37% (1/e) of the peak value (259 mV). This time is about 58 usec, almost exactly the theoretical decay time.